Clock Synchronization in Time Triggered q compare Agains

| | Previous Tutorial | Tutorial 12 | Next Tutorial | | |||

| STM32 Timers Tutorial | |||||||

| STM32 Course Home Page 🏠 | |||||||

In this tutorial, nosotros'll exist discussing the STM32 timers modules in STM32 microcontrollers. There are dissimilar hardware timers in STM32 microcontrollers each tin operate in multiple modes and perform so many tasks. You'll get to know these different hardware variants and their application utilise cases. And we'll start with the timer style in this tutorial, other modes are to be discussed later on.

1. Introduction To Timers Modules

A Timer Module in its most basic form is a digital logic circuit that counts up every clock cycle. More functionalities are implemented in hardware to support the timer module so information technology tin can count upward or down. Information technology can have a Prescaler to divide the input clock frequency by a selectable value. It can as well have circuitry for input capture, PWM indicate generation, and much more than every bit we'll see in this tutorial.

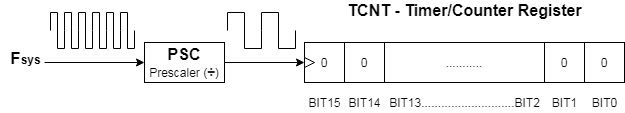

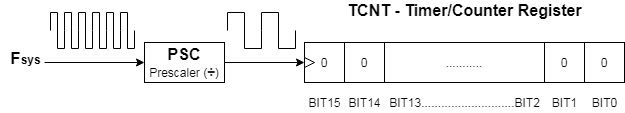

Let'south consider a bones 16-Bit timer similar the ane shown below. Equally a sixteen-Fleck time, it can count from 0 up to 65535. Every clock cycle, the value of the timer is incremented by 1. And equally you can meet, the Fsys is not the frequency that is incrementing the timer module. But information technology gets divided past the Prescaler, then information technology gets fed to the timer.

Basically, in timer mode, the TCNT annals is incremented past 1 each clock cycle @ the following frequency (Fsys/PSC). This means if the Fsys is 80MHz & PSC is one:1024, the TCNT gets incremented by 1 every 12.8μSec. Therefore, if you offset this timer to count from 0 until information technology reaches overflow (at 65535), it will requite you an interrupt signal once every 0.839 Second.

What if I need to set up this timer to give me an interrupt signal one time per i second? I don't want this 0.839Sec time interval in fact. Well, for this reason, there exists a possible hardware feature called preload annals that forces the timer to count from whatever arbitrarily chosen value up to the overflow. So, you no longer have to start counting from zero. Hence, any time interval can be obtained with a timer module.

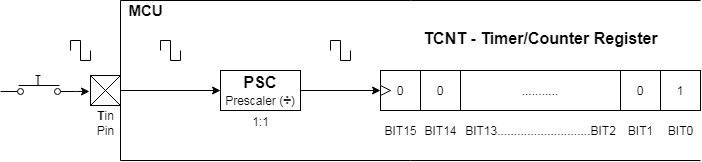

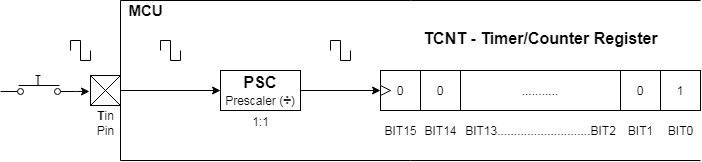

A timer module can too operate in a counter mode where the clock source is not known, information technology's actually an external signal. Maybe from a button button, so the counter gets incremented every rising or falling edge from the button press. This way can exist advantageous in numerous applications every bit we'll discuss hereafter. But for now, consider the following diagram.

Where you can see, the clock signal is now driven from the push button and gets to the timer clock input through the Prescaler. And you lot can capture the information of how many times the button is pressed by simply reading the TCNT register's value.

For more introductory information most Timers Modules & Timer Preloading

2. STM32 Timers Hardware

STMicroelectronics provides some dissimilar versions or variants for the hardware timer modules. STM32 microcontrollers commonly have a handful of each type, nonetheless, some parts may lack ane or more of these hardware timers. So, in this section, I'll highlight those timer modules and their principal features, cake diagram, and things like that.

Just to requite you an overview of the dissimilar available hardware timers in STM32 microcontrollers. So, you can have a better understanding of which type fits in which kind of applications. Which in turn helps you better choice the right MCU function for your project.

2.1 Basic Timers Modules

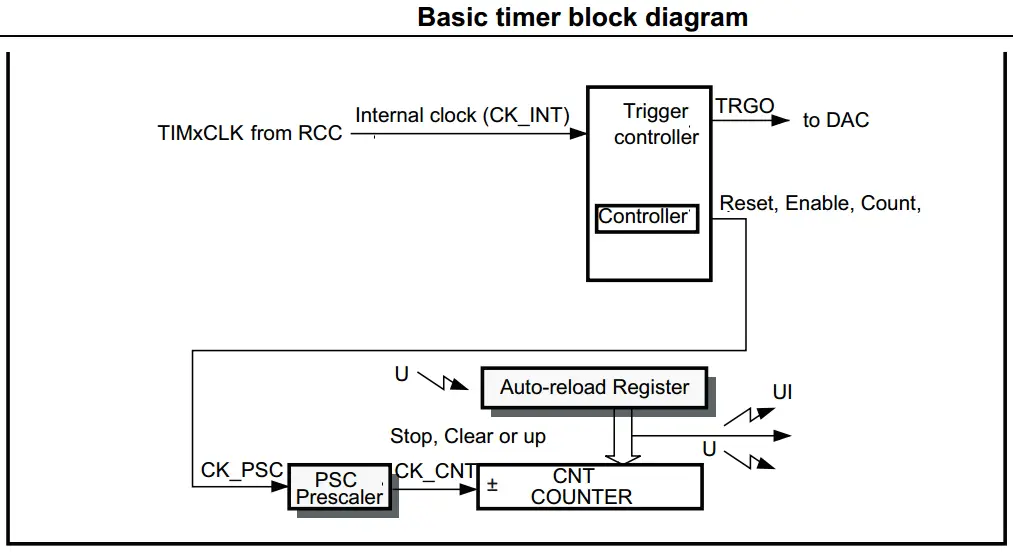

The bones timers consist of a 16-fleck automobile-reload counter driven by a programmable Prescaler. They may be used as generic timers for time-base generation merely they are too specifically used to bulldoze the digital-to-analog converter (DAC). In fact, the timers are internally connected to the DAC and are able to drive it through their trigger outputs. The timers are completely independent and practice not share any resources.

Bones timer features include:

- xvi-bit car-reload upwards-counter

- xvi-chip programmable Prescaler used to split (also "on the fly") the counter clock frequency past any cistron between 1 and 65536

- Synchronization circuit to trigger the DAC

- Interrupt/DMA generation on the update consequence: counter overflow

The primary block of the programmable timer is a 16-bit up-counter with its related motorcar-reload register. The counter clock can exist divided by a Prescaler. The counter, the auto-reload register, and the Prescaler annals can be written or read by software. This is true even when the counter is running. The time-base of operations unit includes:

- Counter Register (TIMx_CNT)

- Prescaler Register (TIMx_PSC)

- Auto-Reload Register (TIMx_ARR)

The auto-reload register is preloaded. The preload register is accessed each time an effort is fabricated to write or read the car-reload register. The contents of the preload register are transferred into the shadow register permanently or at each update issue UEV, depending on the auto-reload preload enable fleck (ARPE).

In counter mode, the counter counts from 0 to the machine-reload value (contents of the TIMx_ARR register), then restarts from 0 and generates a counter overflow event. An update event can be generated at each counter overflow or past setting the UG flake in the TIMx_EGR annals (by software or by using the slave mode controller).

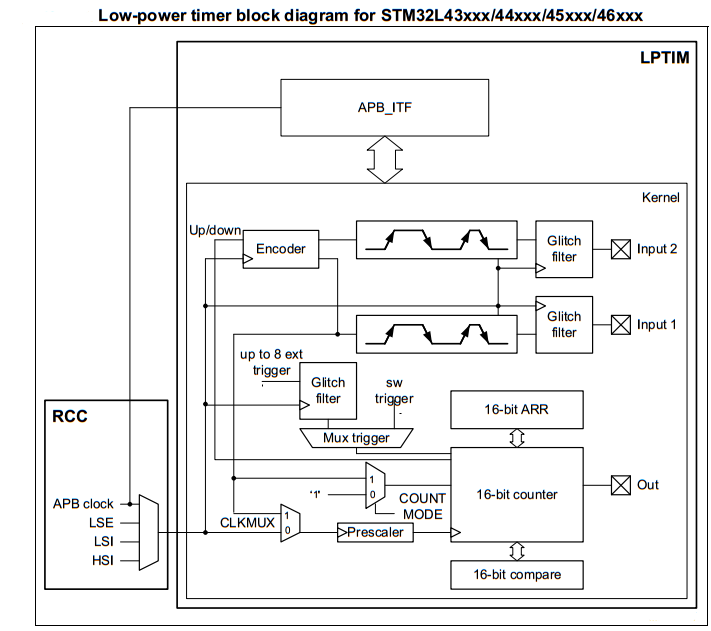

two.2 Low-Ability Timers Modules

The LPTIM is a 16-bit timer that benefits from the ultimate developments in power consumption reduction. Thanks to its diversity of clock sources, the LPTIM is able to keep running in all power modes except for Standby mode. Given its capability to run even with no internal clock source, the LPTIM can exist used every bit a "Pulse Counter" which can be useful in some applications.

Also, the LPTIM capability to wake upwardly the system from low-ability modes makes it suitable to realize "Timeout functions" with extremely low power consumption. The LPTIM introduces a flexible clock scheme that provides the needed functionalities and performance while minimizing power consumption.

The Low-Power Timers (LPTIM) Main Features:

- 16-fleck up-counter

- 3-bit Prescaler with eight possible dividing factors (ane,2,four,viii,16,32,64,128)

- Selectable clock

– Internal clock sources: LSE, LSI, HSI16 or APB clock

– External clock source over LPTIM input (working with no LP oscillator running, used by Pulse Counter application) - 16 bit ARR machine-reload register

- xvi bit compare register

- Continuous/One-shot mode

- Selectable software/hardware input trigger

- Programmable Digital Glitch filter

- Configurable output: Pulse, PWM

- Configurable I/O polarity

- Encoder mode

- Repetition counter

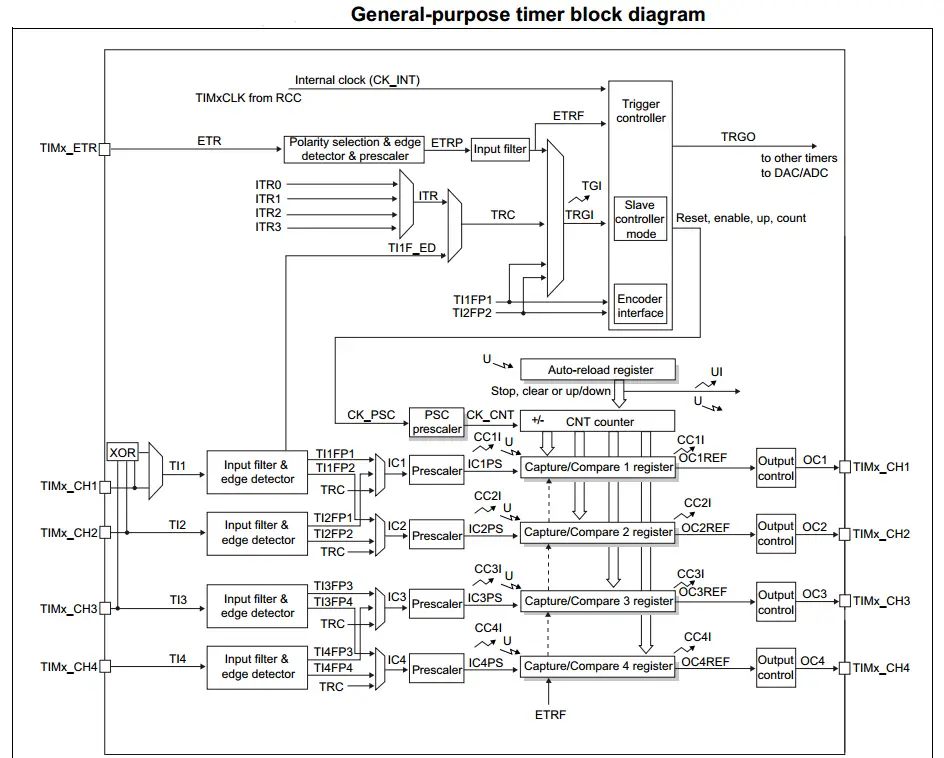

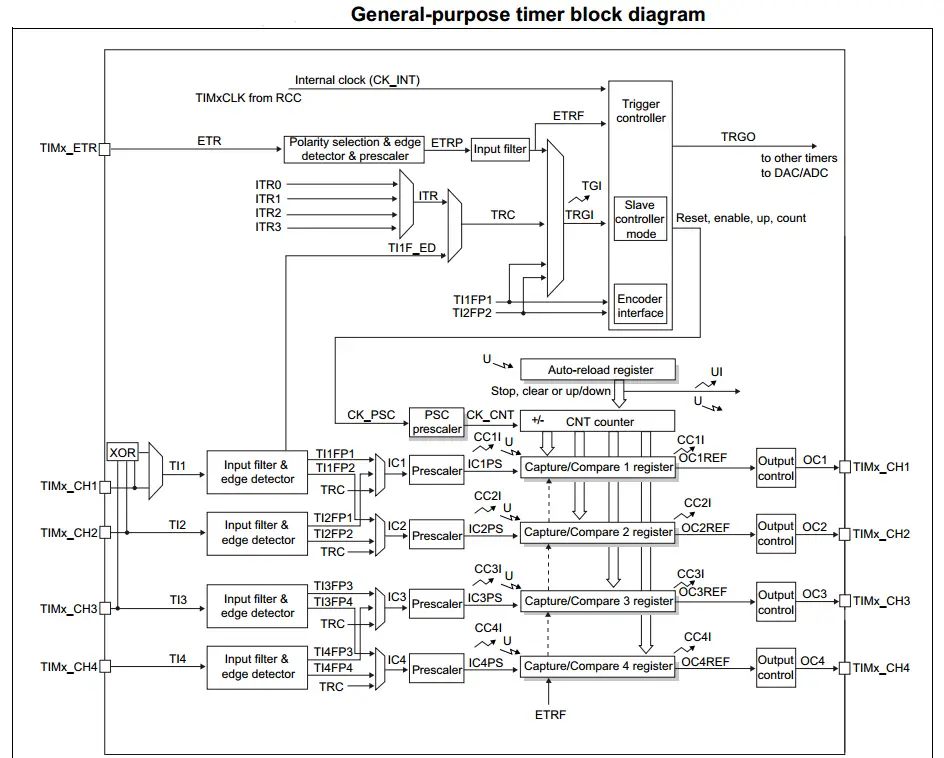

two.three General-Purpose Timers Modules

The general-purpose timers consist of a 16-bit automobile-reload counter driven past a programmable Prescaler. They may be used for a multifariousness of purposes, including measuring the pulse lengths of input signals (input capture) or generating output waveforms (output compare and PWM). Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer Prescaler and the RCC clock controller Prescalers. The timers are completely independent and do non share any resources. They can be synchronized together equally well.

General-purpose TIMx timer features include:

- 16-bit up, down, upwardly/down auto-reload counter.

- 16-scrap programmable Prescaler used to divide (also "on the fly") the counter clock frequency by any gene between 1 and 65536.

- Upwards to 4 independent channels for:

– Input capture

– Output compare

– PWM generation (Border- and Heart-aligned modes)

– One-pulse mode output - Synchronization excursion to control the timer with external signals and to interconnect several timers.

- Interrupt/DMA generation on the following events:

– Update: counter overflow/underflow, counter initialization (by software or internal/external trigger)

– Trigger outcome (counter start, stop, initialization or count by internal/external trigger)

– Input capture

– Output compare - Supports incremental (quadrature) encoder and hall-sensor circuitry for positioning purposes

- Trigger input for an external clock or cycle-by-bike current direction

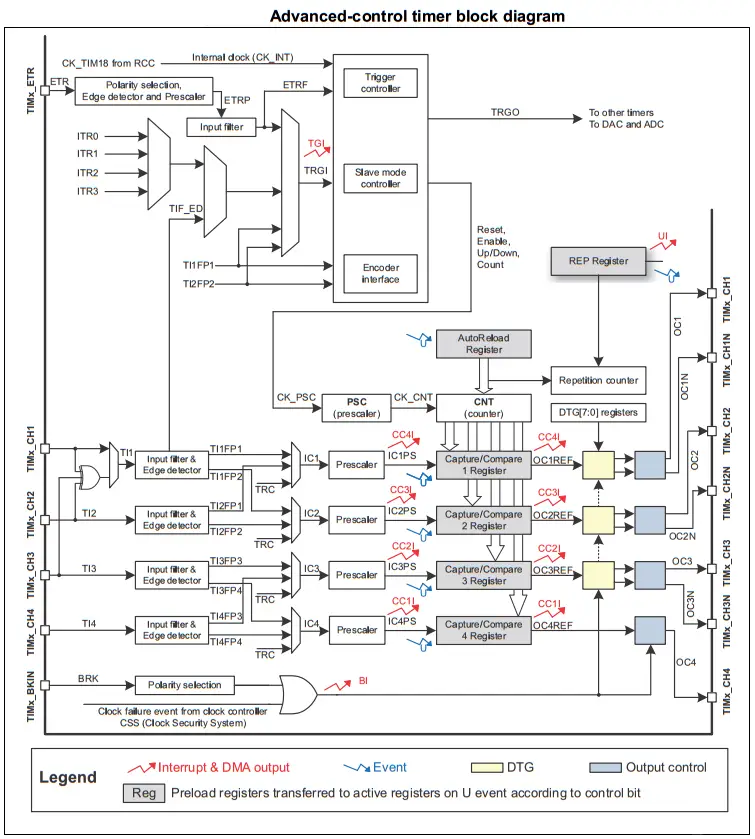

2.4 Advanced-Command Timers Modules

The advanced-control timers consist of a sixteen-bit auto-reload counter driven by a programmable Prescaler. Information technology may be used for a variety of purposes, including measuring the pulse lengths of input signals (input capture), or generating output waveforms (output compare, PWM, complementary PWM with dead-time insertion). Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer Prescaler and the RCC clock controller Prescalers. The avant-garde-control and general-purpose timers are completely independent and do not share any resources. They can exist synchronized together also.

Advanced-Control Timers Features:

- 16-chip upward, downward, up/down auto-reload counter.

- sixteen-chip programmable Prescaler allowing dividing (too "on the fly") the counter clock frequency either past any cistron between 1 and 65536.

- Up to four independent channels for:

– Input Capture

– Output Compare

– PWM generation (Edge and Centre-aligned Manner)

– One-pulse mode output - Complementary outputs with programmable expressionless-fourth dimension

- Synchronization circuit to command the timer with external signals and to interconnect several timers together.

- Repetition counter to update the timer registers simply after a given number of cycles of the counter.

- Interruption input to put the timer'southward output signals in a reset country or in a known state.

- Interrupt/DMA generation on the following events:

– Update: counter overflow/underflow, counter initialization (by software or internal/external trigger)

– Trigger event (counter start, stop, initialization or count by internal/external trigger)

– Input capture

– Output compare

– Suspension input - Supports incremental (quadrature) encoder and hall-sensor circuitry for positioning purposes

- Trigger input for an external clock or wheel-by-cycle current direction

2.five Loftier-Resolution Timers Modules

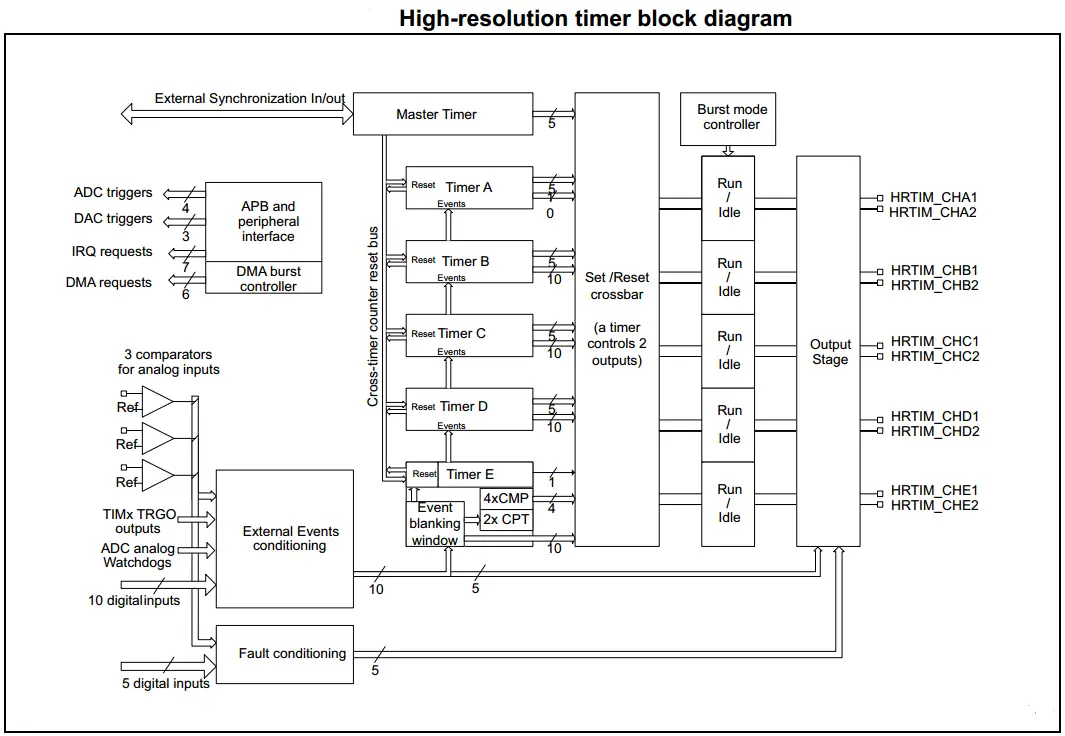

The high-resolution timer tin generate up to 10 digital signals with highly accurate timings. It is primarily intended to bulldoze ability conversion systems such every bit switch-mode power supplies or lighting systems merely can be of general-purpose usage, whenever a very fine timing resolution is expected (upwards to 217pSec).

For control and monitoring purposes, the timer has also timing measure capabilities and links to built-in ADC and DAC converters. Last, it features a light-load management mode and is able to handle various fault schemes for safe shut-down purposes.

Loftier-Resolution Timers (HRTIM) Features Include:

- High-resolution timing units

– 217 ps resolution, compensated against voltage and temperature variations

– Loftier-resolution available on all outputs, possibility to adjust duty-cycle, frequency and pulse width in the triggered one-pulse manner

– 6 xvi-bit timing units (each 1 with an independent counter and four compare units)

– 10 outputs that can be controlled by any timing unit of measurement, up to 32 fix/reset sources per channel

– Modular architecture to accost either multiple independent converters with 1 or 2 switches or few big multi-switch topologies - Multiple links to born analog peripherals

– 4 triggers to ADC converters

– 3 triggers to DAC converters

– 3 comparators for analog betoken conditioning - Multiple HRTIM instances can be synchronized with external synchronization inputs/outputs

- Versatile output stage

– High-resolution Deadtime insertion (down to 868 pSec)

– Programmable output polarity

– Chopper mode - Burst mode controller to handle light-load operation synchronously on multiple converters

- 7 interrupt vectors, each 1 with up to 14 sources

- 6 DMA requests with up to 14 sources, with a burst way for multiple registers update

3. STM32 Timers Modes OF Functioning

An STM32 timer module tin can operate in any of the following modes, however, you should not assume that a given timer does back up all of these modes. Instead, y'all'll have to bank check the datasheet to figure out which modes are supported by which timers. Every bit nosotros've seen earlier, at that place are many groups of timers which include: General-Purpose, Low-Power, Loftier-Resolution, Advanced-Control timers. Each of which does support a multiple of the following modes, however, some timers do support nigh of the operating modes.

In this section, we'll become simply a brief description of each mode of performance. How it works and what sort of applications it fits for. Each mode volition be discussed in-depth with practical LAB experiments in future tutorials. But for today, we'll get into Timer Mode in section4 and do its LAB in the next tutorial. Other modes will be coming afterwards on in this series of tutorials.

three.1 Timer Mode

In timer fashion, the timer module gets clocked from an internal clock source with a known frequency. Hence the clocking frequency is known, the overflow fourth dimension can also be calculated and controlled by the preload register to get any arbitrarily chosen fourth dimension interval. Each timer overflow, the timer signals the CPU with an interrupt that indicates the end of the specified time interval.

This mode of operation is usually used to get a specific operation done each specific time interval. And to achieve timing & sync between various tasks and events in the system. It tin also supervene upon delays in diverse situations for better system response.

iii.2 Counter Style

In counter mode, the timer module gets clocked from an external source (timer input pin). Then the timer counts up or down on each rise or falling edge of the external input. This manner is really helpful in numerous situations when you need to implement a digital counter without polling input pins or periodically reading a GPIO or continuously interrupt the CPU if you've chosen to claw it up to an EXTI pin.

You tin actually monitor the counter value divergence each time interval to tell how many pulses did occur or what was the frequency of information technology. Such a style tin can exist advantageous in many situations like this. And more examples are to come up in upcoming tutorials.

3.3 PWM Mode

In PWM mode, the timer module is clocked from an internal clock source and produces a digital waveform on the output channel pin called the PWM signal. By using output compare registers (OCR), the incrementing timer's register value is constantly compared confronting this OCR register. When a match occurs the output pin state is flipped until the end of the period and the whole process is repeated.

The timer in PWM mode will produce a PWM signal at the specified frequency the user chose. The duty wheel is as well programmatically controlled past its register. The PWM resolution is affected by the desired FPWMand other factors as we'll see in the defended tutorials for PWM generation.

3.iv Advanced PWM Mode

The advanced PWM signal generation refers to the hardware ability to control more parameters and add some hardware circuitry to support extra features for the PWM indicate generation. Which includes:

- The ability to produce a complementary PWM betoken that is typically the same every bit the PWM on the primary channel but logically inverted (high portion becomes low and vice versa).

- The ability to inject dead-time band in the PWM signal for motor driving applications to prevent shoot-through currents that upshot from PWM signals overlapping.

- The power to perform auto-shutdown for the PWM signal, it's also chosen "auto brake" which an of import feature for safe-critical applications.

- And the power to stage-adjust the PWM point, and much more than! All of this is referred to as advanced-PWM control.

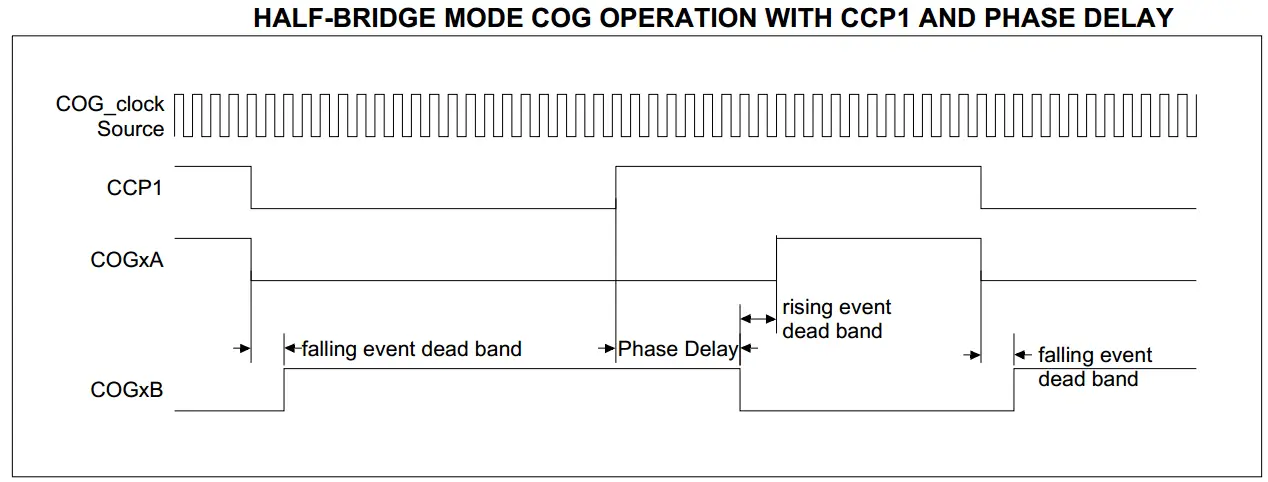

Hither is an example for PWM channels with complementary waveform output, with dead-band inserted, and stage-delay aligning. A typical control indicate in half-bridge mode.

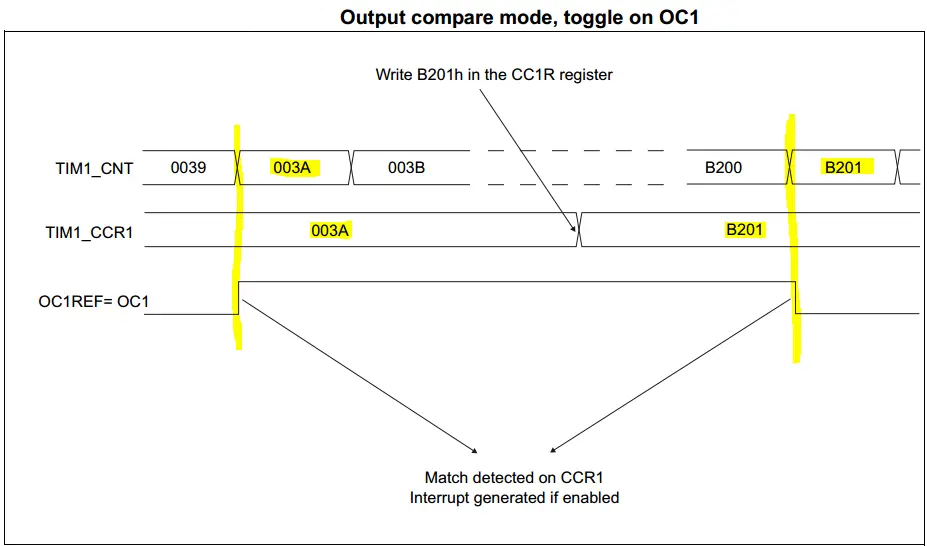

iii.five Output Compare Mode

In output compare mode, a timer module controls an output waveform or indicates when a menstruation of time has elapsed. When a match is detected between the output compare register (OCR) and the counter, the output compare function assigns the corresponding output pin to a programmable value defined past the output

compare mode defined by the programmer.

The output compare pin can be driven high, low, toggles its sate, or stay unchanged. This is determined past the programmer equally per the application requirements. This mode of operation can exist extremely advantageous for generating timing signals and output driving in many applications every bit we'll see in future tutorials.

Here is an example for a counting timer in output compare mode. Notation when the output state is changed (toggled) and the value in the OCR (compare register TIM1_CCR1).

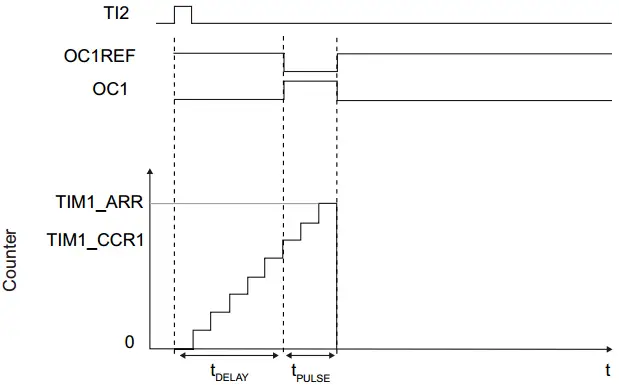

3.6 I-Pulse Style

One-pulse mode (OPM) is a particular case of the previous modes. Information technology allows the counter to be started in response to a stimulus and to generate a pulse with a programmable length after a programmable delay. Starting the counter tin exist controlled through the slave mode controller. Generating the waveform can be done in output compare mode or PWM mode.

A pulse can be correctly generated merely if the compare value is different from the counter initial value. Before starting (when the timer is waiting for the trigger), the configuration must be CNT<CCRx ≤ ARR (in detail, 0<CCRx). For example, you may want to generate a positive pulse on OC1 with a length of t PULSE and after a delay of t DELAY equally soon as a positive border is detected on the TI2 input pivot.

three.7 Input Capture Mode

In Input capture mode, the Capture/Compare Registers (TIMx_CCRx) are used to latch the value of the counter later a transition detected past the respective ICx signal. When a capture occurs, the corresponding CCXIF flag (TIMx_SR register) is gear up and an interrupt or a DMA request can be sent if they are enabled.

This mode is extremely important for external signal measurement or external event timing detection. The current value of the timer counts is captured when an external issue occurs and an interrupt is fired. And so, we can apply this feature for a broad range of measurement applications.

An awarding instance is an ultrasonic sensor that measures the altitude and sends the information as a pulse to your microcontroller. By measuring the pulse width time, you lot can detect out the distance reading. This can be achieved by using the input capture unit (ICU) inside the timer module.

3.8 Encoder Mode

In the encoder interface mode, the timer module operates every bit a digital counter with two inputs. The counter is clocked past each valid transition on both input pins. The sequence of transitions of the two inputs is evaluated and generates count pulses likewise as the direction signal. Depending on the sequence the counter counts upward or downwards. So you don't have to detect these pulses individually and see which came first to find rotation management and this kind of work. Now, all of this is washed by hardware thanks to the encoder way hardware support.

The timer, when configured in Encoder Interface mode provides data on the sensor'southward current position. The user can obtain dynamic information (speed, dispatch, deceleration) past measuring the catamenia between two encoder events using a second timer configured in capture way. The output of the encoder which indicates the mechanical cypher can be used for this purpose. Depending on the time betwixt ii events, the counter can also be read at regular times.

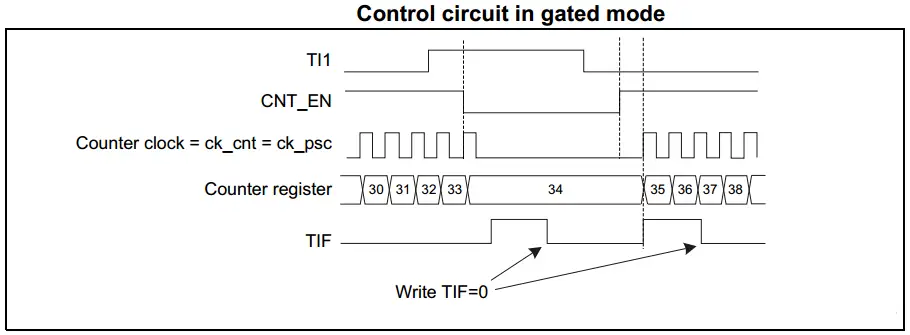

3.9 Timer Gate Mode

In timer gated mode, a timer module is also said to be working in "slave manner". Where it just counts equally long as an external input pin is held high or low. This input pin is said to be the timer gate that allows the timer to count or not at all.

This fashion tin can be used in a wide range of applications and point measurements. It can assistance yous measure extremely short pulses with a very high resolution. And as well trigger the timer to count on external events from sensors or other MCUs.

The counter starts counting on the internal clock equally long every bit TI1 is low and stops as before long as TI1 becomes high. The TIF flag in the TIMx_SR register is set both when the counter starts or stops. The delay betwixt the rising edge on TI1 and the actual stop of the counter is due to the resynchronization circuit on TI1 input.

three.10 Timer DMA Burst Mode

The STM32 timers, not all of them, have the adequacy to generate multiple DMA requests upon a single event. The main purpose is to be able to re-program part of the timer multiple times without software overhead, merely information technology tin can likewise be used to read several registers in a row, at regular intervals.

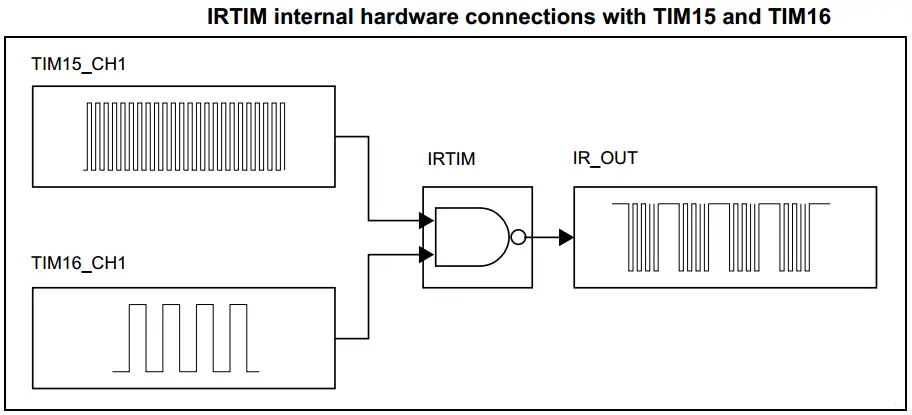

3.11 IRTIM Infrared Mode

An infrared interface (IRTIM) for remote control tin can be used with an infrared LED to perform remote control functions. Information technology uses internal connections with TIM15 and TIM16 as shown in the diagram downward beneath. To generate the infrared remote control signals, the IR interface must exist enabled and TIM15 channel one (TIM15_OC1) and TIM16 channel i (TIM16_OC1) must be properly configured to generate correct waveforms. The infrared receiver can be implemented easily through a basic input capture manner.

All standard IR pulse modulation modes can be obtained by programming the two-timer output compare channels. TIM15 is used to generate the loftier-frequency carrier point, while TIM16 generates the modulation envelope. The infrared office is output on the IR_OUT pivot. The activation of this function is washed through the GPIOx_AFRx annals by enabling the related alternate function bit.

4. STM32 Timers – Timer Style

After this long overview of the STM32 timers hardware variants and the timers' possible modes of operations, nosotros'll just focus on i of them for the rest of this tutorial. Which is going to exist the very basic one, the "timer mode". So, we'll discuss the timer style operation in-depth and nosotros'll follow this up past a practical LAB in the adjacent tutorial. After, we tin can movement on to another mode of performance (counter, ICU, PWM, etc).

iv.1 Block Diagram

For this tutorial, we'll exist working with a gerneral-purpose timer. And hither is its logic block diagram.

4.2 Functional Description

4.ii.1 Fourth dimension-Base Unit

The main block of the programmable timer is a xvi-flake counter with its related automobile-reload register. The counter can count up, downward, or both upward and down. The counter clock can exist divided by a Prescaler. The counter, the car-reload register, and the Prescaler annals can be written or read by software. This is true even when the counter is running. The fourth dimension-base of operations unit includes:

- Counter Annals (TIMx_CNT)

- Prescaler Register (TIMx_PSC):

- Auto-Reload Register (TIMx_ARR)

The car-reload register is preloaded. Writing to or reading from the motorcar-reload register accesses the preload register. The content of the preload annals is transferred into the shadow register permanently or at each update effect (UEV), depending on the auto-reload preload enable bit (ARPE) in the TIMx_CR1 register. The update event is sent when the counter reaches the overflow.

4.ii.2 Timer Prescaler

The Prescaler can dissever the counter clock frequency by whatever factor betwixt 1 and 65536. Information technology is based on a sixteen-bit counter controlled through a 16-bit annals (in the TIMx_PSC register). Information technology can be inverse on the wing every bit this command register is buffered. The new Prescaler ratio is taken into account at the next update result.

4.three Applications Examples

The timer module in timer mode tin be used to generate a time filibuster interval betwixt specific events. Or to repeatedly perform a specific task each specific fourth dimension interval. And as well to mensurate the time between predefined events. Then, a timer tin generate or measure fourth dimension intervals based on the internal clock and the Prescaler which together defines the resolution of the timer tick fourth dimension.

iv.4 Different Possible Configurations

When you're configuring a timer module to operate in timer fashion, you should be concerned to gear up the following configurations equally per your awarding requirements.

The timer time interval, which is a combination of the following settings:

- The timer clock source frequency

- The Prescaler value

- The time counting mode (up or down)

- Auto-Reload annals value

- Autor preload enable/disable

- Overflow interrupt enable/disable

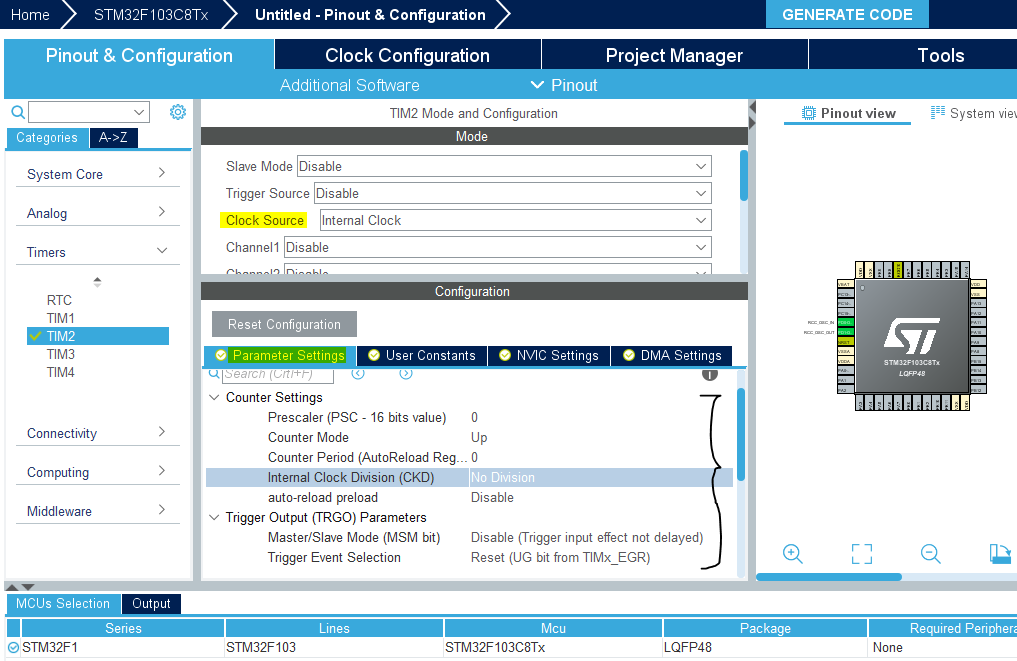

iv.5 CubeMX Timer Configurations Options

Hither is a screenshot from the CubeMX software tool indicating the possible configurations for the TIM2 module which is a general-purpose timer module. And this is the one nosotros'll exist using in the side by side practical LAB and will write application lawmaking to test it.

4.vi STM32 Timer Interrupts

General-Purpose STM32 Timers tin can generate an Interrupt/DMA betoken on the following events:

- Update: counter overflow/underflow, counter initialization (by software or internal/external trigger)

- Trigger event (counter commencement, stop, initialization or count by internal/external trigger)

- Input capture

- Output compare

For our applications in the following tutorial/LAB, we'll be using the overflow interrupt signal to toggle an LED or whatever to test the timer functionality and timing correctness.

And That'southward information technology For This Tutorial .. In The Next Few Tutorials, We'll Exercise Some LABs To Exam all other modes of operation for STM32 Timers modules (counter, input capture, PWM, etc). And so, Get Ready For That!

And Delight, Consider Supporting The Content Past SHARING It On Socials Or Via Patreon.

| | Previous Tutorial | Tutorial 12 | Adjacent Tutorial | | |||

Source: https://deepbluembedded.com/stm32-timers-tutorial-hardware-timers-explained/

0 Response to "Clock Synchronization in Time Triggered q compare Agains"

Postar um comentário